After reaching the count of “1001”, the counter recycles back to “0000”. So I am made this as a blog post to help my fellow budding – engineers who would require this thing in future!Ī Decade synchronous counter can be built using synchronous binary counters to produce a count sequence from 0 to 9.Ī standard binary counter can be converted to a decade (decimal 10) counter with the aid of some additional logic to implement the desired state sequence. But it was not there (implementation through JK Flip – Flop).

#Falling edge triggered flip flop vhdl code

After I tried coding it myself, but after many efforts, I finally searched for code on Google. This was given to me as an end – semester lab project which I was not able to make.

#Falling edge triggered flip flop vhdl how to

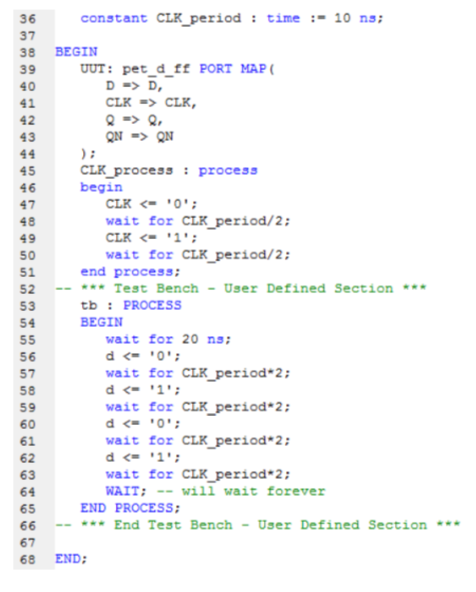

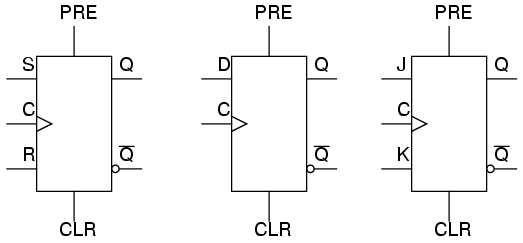

How to avoid unintentional latch inference in VHDL? As shown in Figure 1 (a), a basic positive-level D latch has three terminals: data input d, data output q, and a control input c. How many terminals does a latch have in VHDL?Ī latch is a level-sensitive memory element. The D flip-flop is an edge triggered device which transfers input data to Q on clock rising or falling edge. The difference between a D-type latch and a D-type flip-flop is that a latch does not have a clock signal to change state whereas a flip-flop always does. What is difference between D latch and D FF? To avoid latch inference, there are two possible solutions: we can either assign values to all three outputs in every branch of the “if” statement, or we can assign the outputs a default value before the “if” statement. Often they add significant routing delays and can cause your design to fail to meet timing. The reason that latches should never be used is twofold: They can be very difficult for the FPGA tools to create properly. It was stated that latches should never be used in your FPGA design. It can be thought of as a basic memory cell.

The D stands for ‘data’ this flip-flop stores the value that is on the data line.

What does D latch stand for?Ī D Flip Flop (also known as a D Latch or a ‘data’ or ‘delay’ flip-flop) is a type of flip flop that tracks the input, making transitions with match those of the input D. They may lead to combinatorial feedback – routing of the output back to the input – which can be unpredictable. Latches can lead to timing issues and race conditions. The inferred latch is a transparent latch.

This causes the synthesis to make the logical decision to “hold” the value of a signal when not told to do anything else with it. Latches are inferred in VHDL by using the IF statement without its matching ELSE. This type of flip-flop is referred to as an SR flip-flop. Each flip-flop has two outputs, Q and Q’, and two inputs, set and reset. How are flip flops different from latches in VHDL?Ī flip-flop circuit can be constructed from two NAND gates or two NOR gates.Why is the D latch called a transparent latch?.How to avoid unintentional latch inference in VHDL?.How many terminals does a latch have in VHDL?.What is difference between D latch and D FF?.

0 kommentar(er)

0 kommentar(er)